Notes04:GPIO功能框图详解

创始人

2025-05-31 14:22:56

0次

GPIO功能框图详解

- 野火霸道开发板学习笔记

- 信息说明

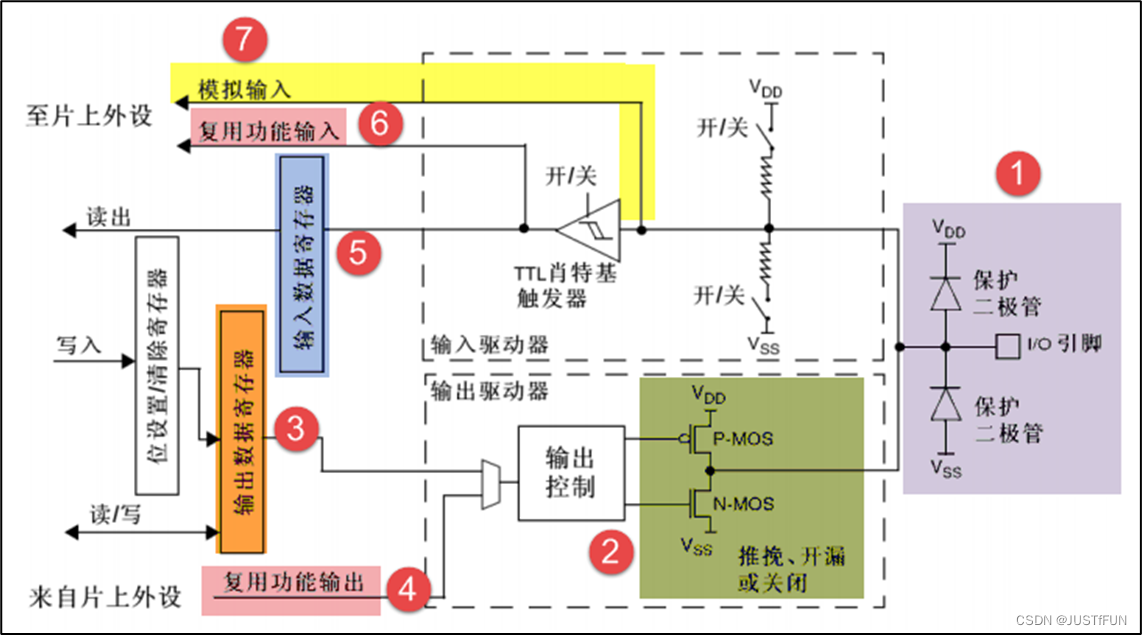

- GPIO功能框图

- 输出部分

- 推挽输出

- 推挽输出模型分析

- 推挽输出总结

- 开漏输出

- 开漏输出模型分析

- 开漏输出总结

- 输出数据寄存器(ODR)

- 位设置清除寄存器(BSRR)

- 位清除寄存器(BRR)

- 输入部分

- 输入数据寄存器(IDR)

- TTL肖特基触发器部分

- 模型分析

- 上拉/下拉输入的配置

- TTL电平标准

- CMOS电平标准

- RS232标准

- GPIO输出初始化顺序

野火霸道开发板学习笔记

信息说明

- 开发板: 野火霸道V2

- 芯片型号: STM32F103ZET6

- 下载器型号: 野火fireDAP下载器(高速版)

- 软件环境: Keil5(MDK-ARM V5.15)

- 芯片包型号: Keil.STM32F1xx_DFP.1.1.0 注: 亲测版本2.4.0不可用

- 操作系统 : Win11

GPIO功能框图

输出部分

GPIO框图2号区域由CRL和CRH配置

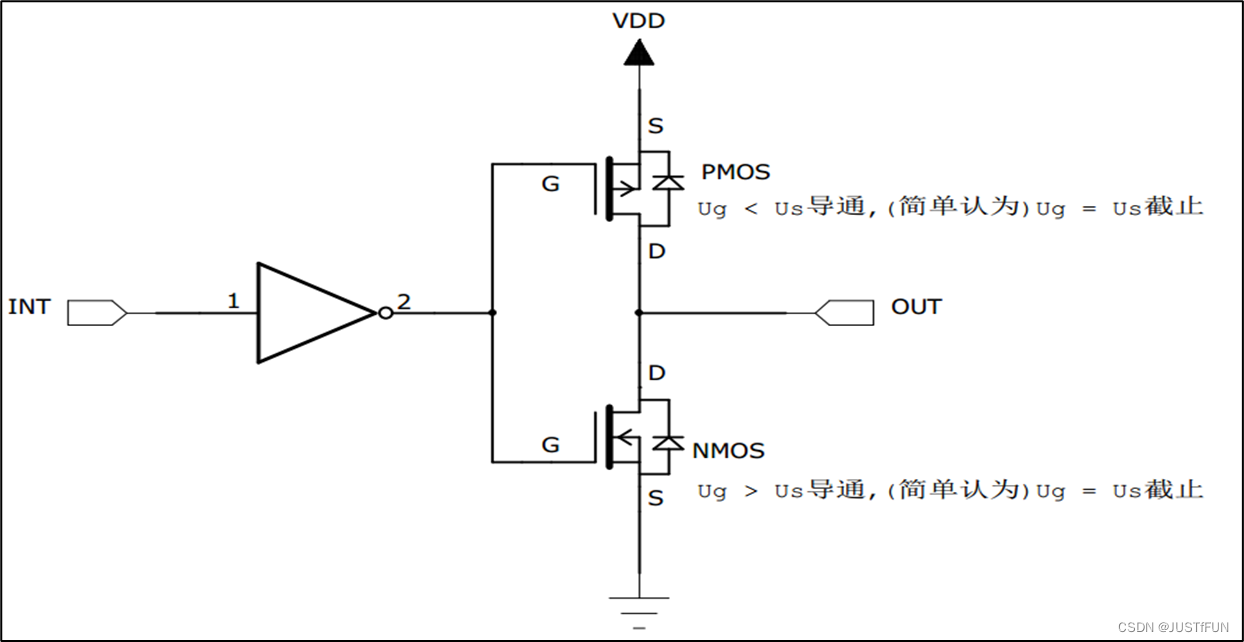

推挽输出

推挽输出模型分析

- 当INT = 1时, 经过反相器在2位置处为0, 此时对于PMOS管来说, Ug为低电平, Us = VDD, 故 Ug < Us, PMOS导通, S->D有电流, OUT = VDD, 输出高电平1

- 当INT = 0时, 经过反相器在2位置处为1, 此时对于NMOS管来说, Ug为高电平, Us = GND, 故 Ug > Us, NMOS导通, D->S有电流, OUT = GND, 输出低电平0

推挽输出总结

- 可以输出高低电平, 用于连接数字器件, 高电平由VDD决定, 低电平由VSS决定

- 推挽结构指两个三极管(多用MOS管)受两路互补的信号控制, 总是在一个导通的时候另外一个截止, 优点 : 开关效率效率高, 电流大,驱动能力强

- 输出高电平时, 电流输出到负载, 叫灌电流, 可以理解成推, (电流方向 : S->D); 输出低电平时, 负载电流流向芯片, 叫拉电流, 即挽**(电流方向 : D->S)**

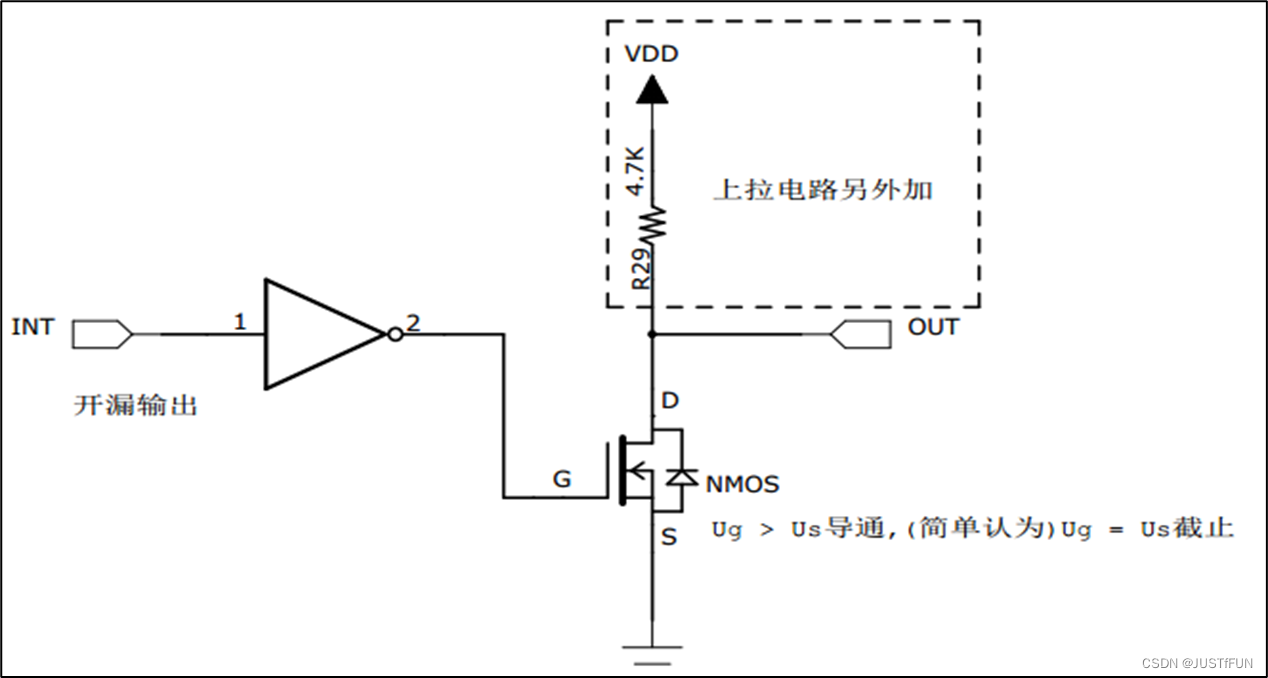

开漏输出

开漏输出模型分析

- 当 INT = 1 时, 1处为1, 经反相器后2处为0, Ug = Us, NMOS管截止, 当接入上拉电阻时, OUT = 1, 输出高电平, 若不加则为高阻态

- 当 INT = 0 时, 1处为0, 经反相器后2处为1, Ug > Us, NMOS管导通, OUT = 0, 输出低电平

开漏输出总结

- 只能输出低电平, 不能输出高电平 (PMOS管不工作)

- 如果要输出高电平, 则需要外接上拉电阻

- 开漏输出具有"线与"功能, 一个为低, 全部为低, 多用于I2C和SMBUS总线

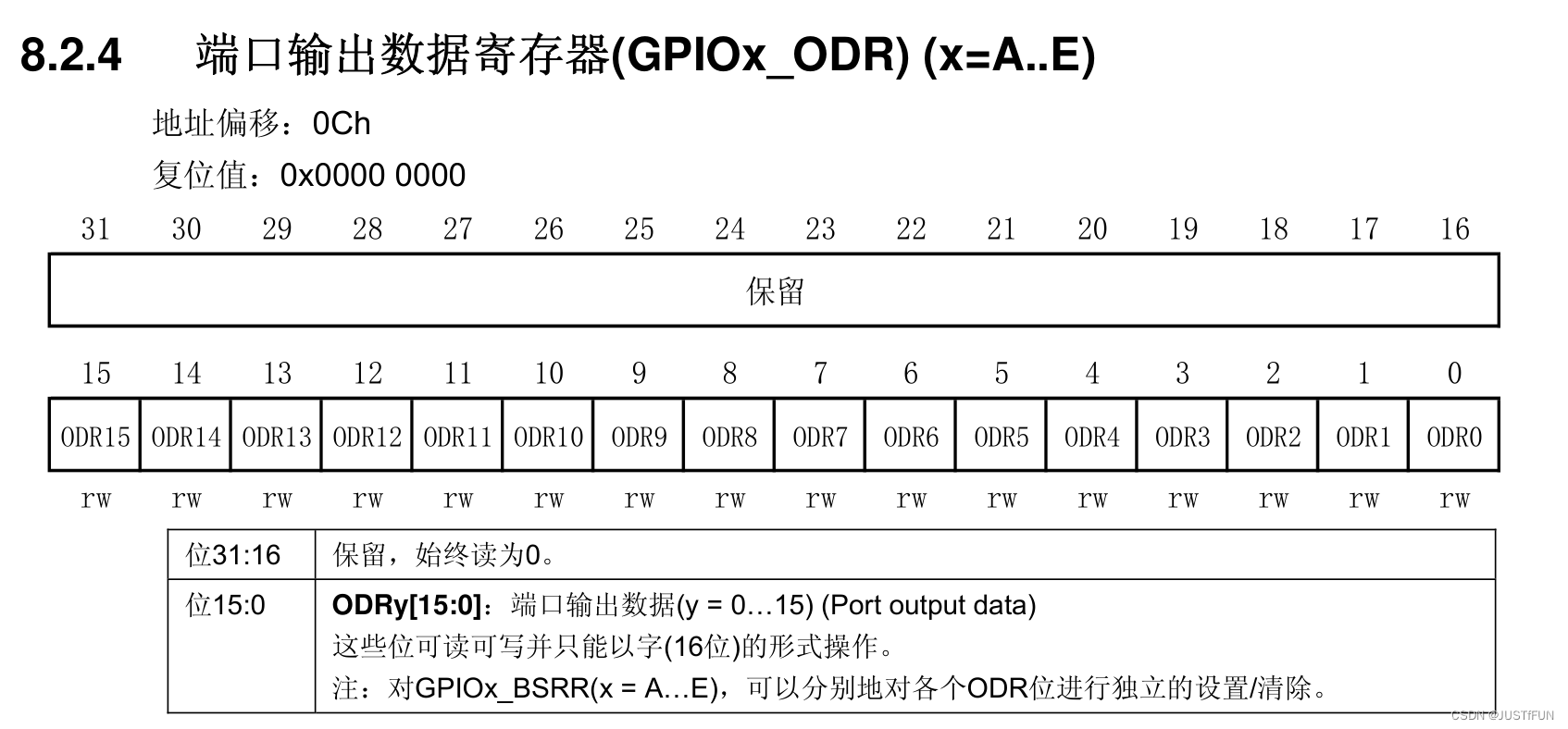

输出数据寄存器(ODR)

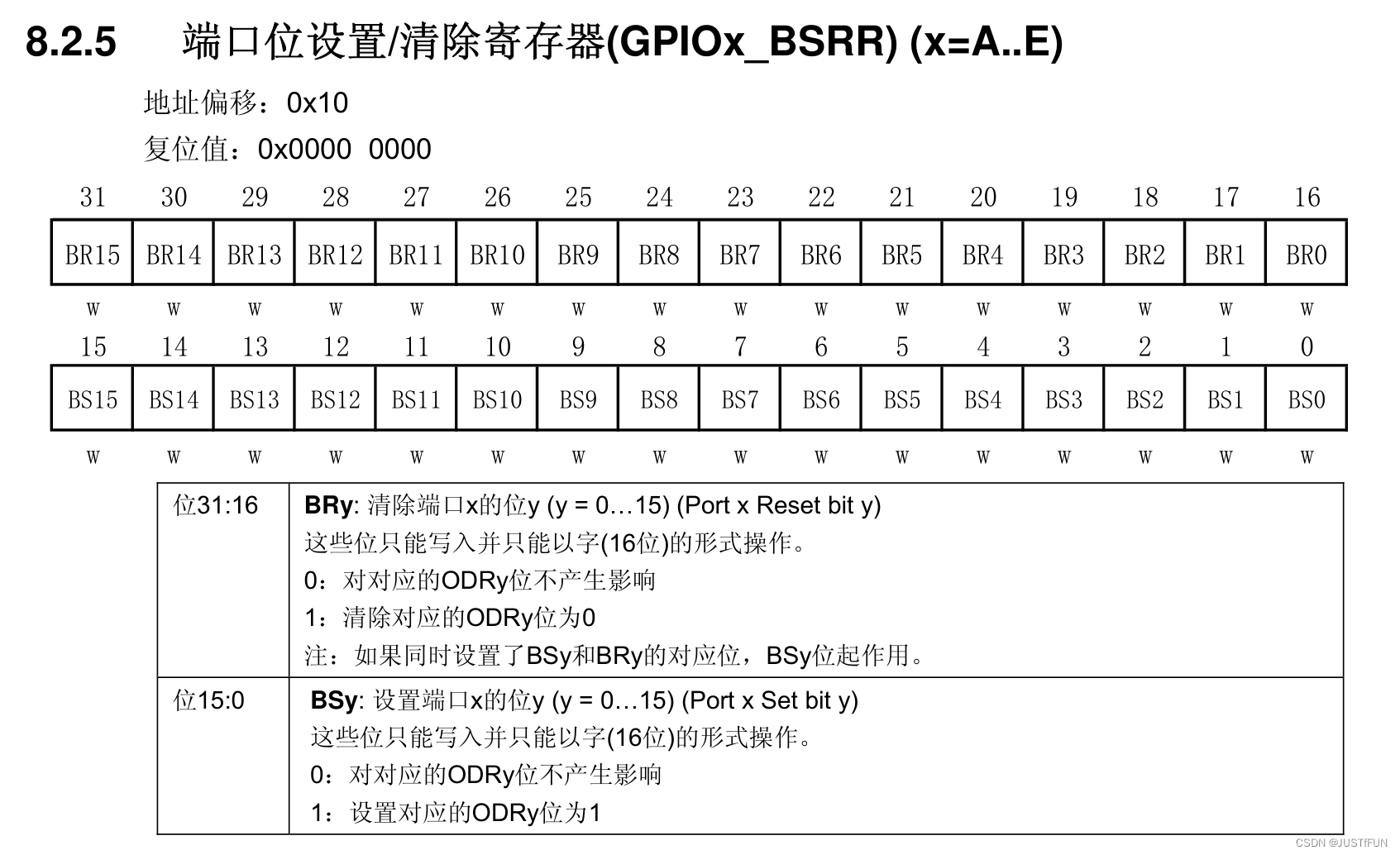

位设置清除寄存器(BSRR)

BSRR寄存器实际上还是调用了ODR寄存器

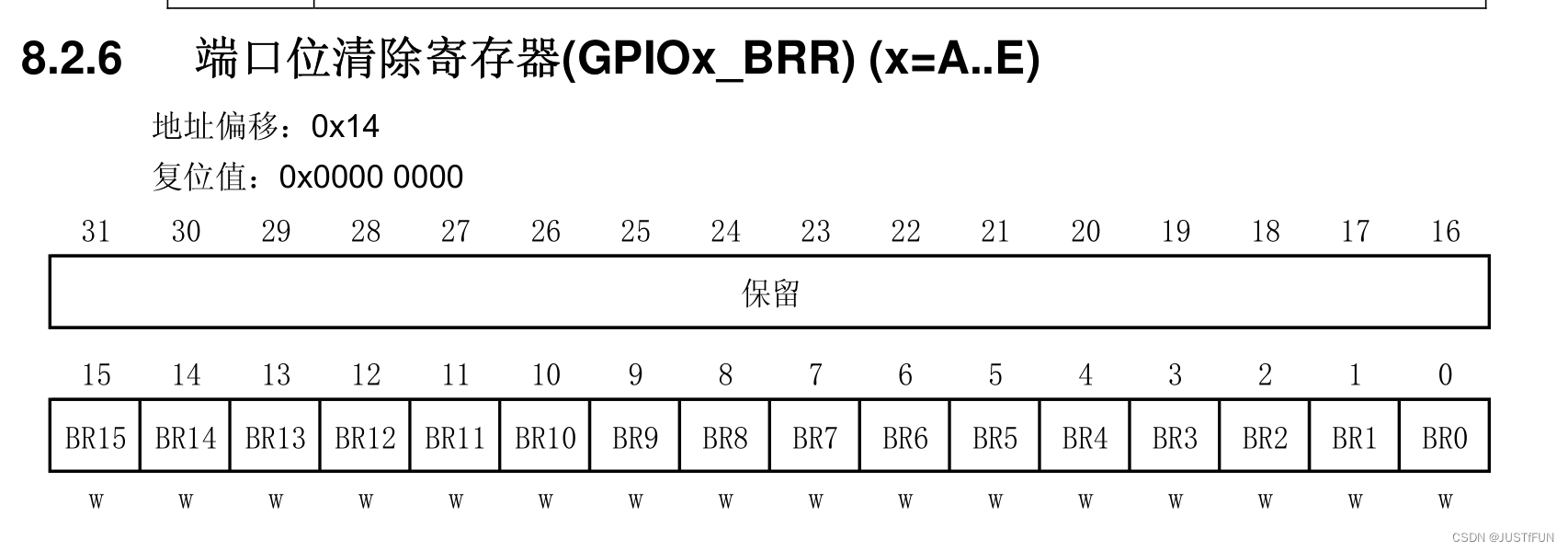

位清除寄存器(BRR)

输入部分

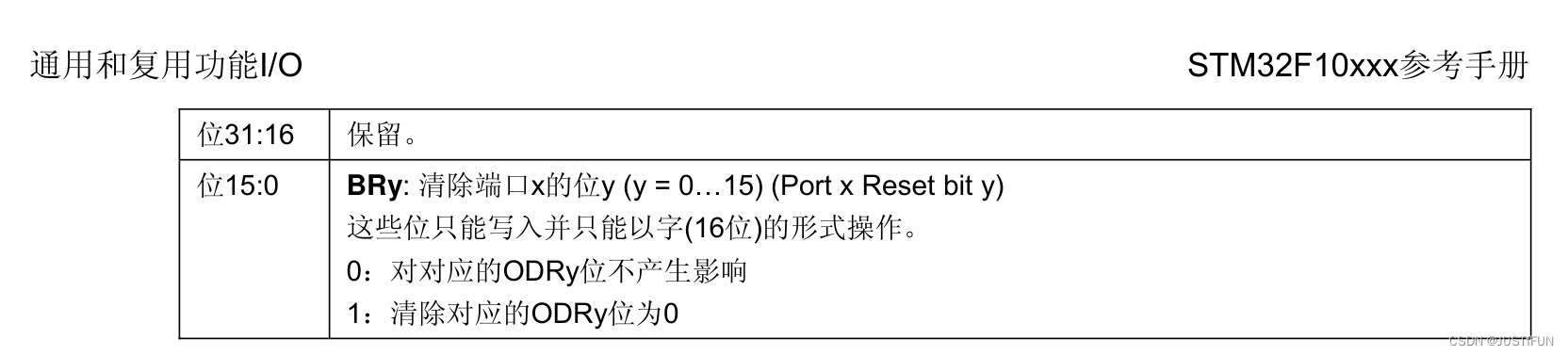

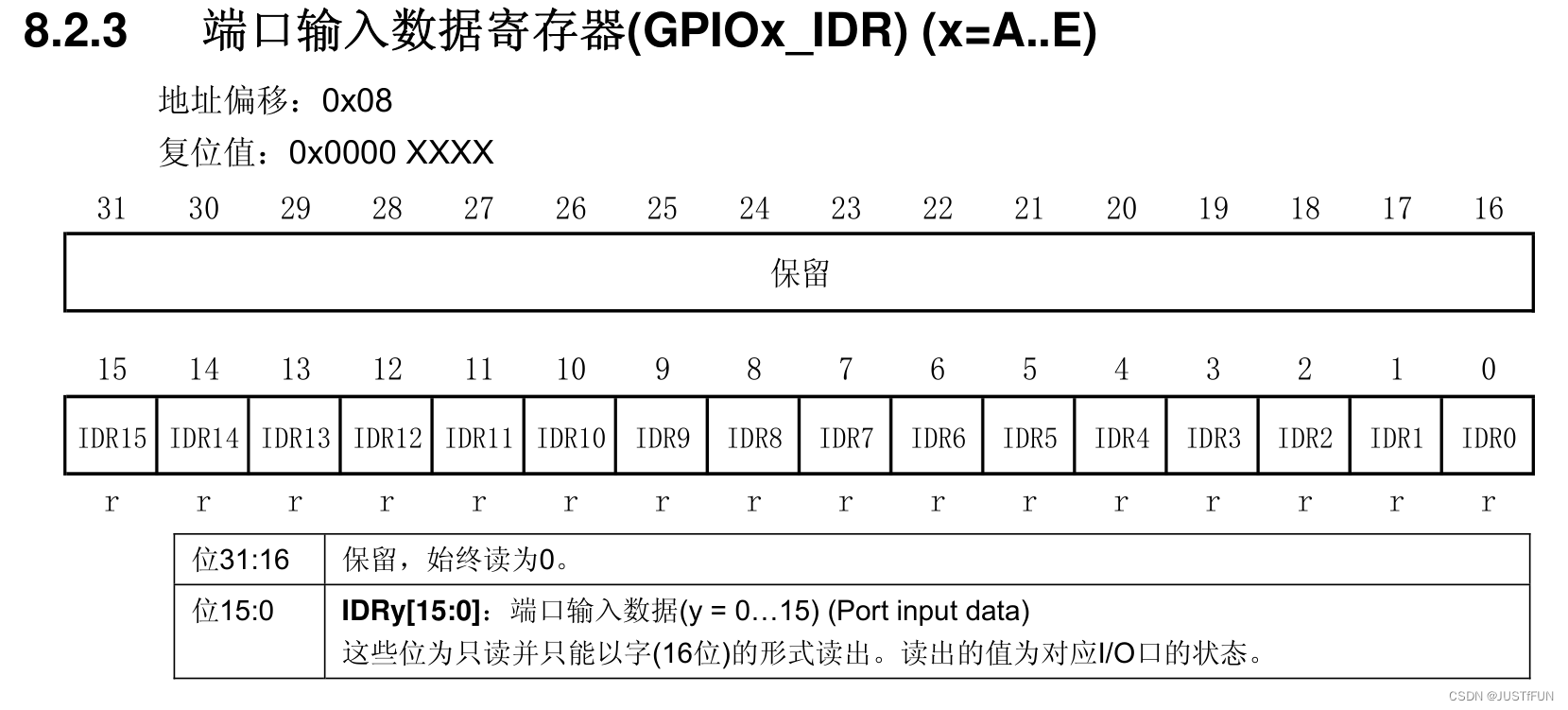

输入数据寄存器(IDR)

IDR 可以监控到 ODR 的数据

TTL肖特基触发器部分

模型分析

- I/O 口电平经上拉/下拉输入, 若为3.3V高电平

- TTL肖特基触发器起到门禁作用*(输入时, > 2.0V为高电平)*, 将模拟信号转化为数字信号, 即将3.3V 转换为逻辑高电平

- 转换后的数字信号进入输入数据寄存器(IDR)

- 若为复用功能输入, 则数字信号不进入IDR

- 若为模拟输入, 则不通过TTL肖特基触发器, 而直接传递模拟信号

上拉/下拉输入的配置

- 由 CRL/CRH 配置成上拉/下拉输入模式

- 通过 BSRR 软件配置具体为上拉还是下拉输入模式

TTL电平标准

- 输出: L : < 0.8V; H: > 2.4V

- 输入: L : < 1.2V; H: > 2.0V

TTL器件输出低电平要小于0.8V, 高电平要大于2.4V; 对于输入, 低于1.2V就认为是0, 高于2.0V就认为是1

TTL电平输入低电平的噪声容限为(0.8 - 0) / 2 = 0.4V, 高电平的噪声容限为 (5 - 2.4) / 2 = 1.3V

CMOS电平标准

- 输出 : L: < 0.1 * Vcc; H: > 0.9 * Vcc

- 输入: L: < 0.3 * Vcc; H : > 0.7 * Vcc

由于CMOS电源采用12V, 则输入低于3.6V为低电平, 噪声容限为1.8V, 高于 3.5V为高电平, 噪声容限为1.8V. 比TTL有更高的噪声容限

RS232标准

- 逻辑1的电平为 -3 ~ -15V

- 逻辑0的电平为 +3 ~ +15V

RS232标准下电平的定义反相了一次

GPIO输出初始化顺序

- 选定具体的GPIO*(影响到后续寄存器具体配置哪一位)*

- 配置GPIO工作模式**(CRL和CRH寄存器)**

- 控制GPIO输出高低电平**(ODR, BRR和BSRR)**

相关内容

热门资讯

保存时出现了1个错误,导致这篇...

当保存文章时出现错误时,可以通过以下步骤解决问题:查看错误信息:查看错误提示信息可以帮助我们了解具体...

汇川伺服电机位置控制模式参数配...

1. 基本控制参数设置 1)设置位置控制模式 2)绝对值位置线性模...

不能访问光猫的的管理页面

光猫是现代家庭宽带网络的重要组成部分,它可以提供高速稳定的网络连接。但是,有时候我们会遇到不能访问光...

不一致的条件格式

要解决不一致的条件格式问题,可以按照以下步骤进行:确定条件格式的规则:首先,需要明确条件格式的规则是...

本地主机上的图像未显示

问题描述:在本地主机上显示图像时,图像未能正常显示。解决方法:以下是一些可能的解决方法,具体取决于问...

表格列调整大小出现问题

问题描述:表格列调整大小出现问题,无法正常调整列宽。解决方法:检查表格的布局方式是否正确。确保表格使...

表格中数据未显示

当表格中的数据未显示时,可能是由于以下几个原因导致的:HTML代码问题:检查表格的HTML代码是否正...

Android|无法访问或保存...

这个问题可能是由于权限设置不正确导致的。您需要在应用程序清单文件中添加以下代码来请求适当的权限:此外...

银河麒麟V10SP1高级服务器...

银河麒麟高级服务器操作系统简介: 银河麒麟高级服务器操作系统V10是针对企业级关键业务...

【NI Multisim 14...

目录 序言 一、工具栏 🍊1.“标准”工具栏 🍊 2.视图工具...